Bryan Hicks

Diode Properties of Nanotube Networks

Applied Physics Capstone Project Report

Physics 492R

7 April 2008

Advisor: Dr. David Allred

#### **Diode Properties of Nanotube Networks**

Bryan Hicks<sup>1</sup>, Stephanie Getty<sup>2</sup>, and David Allred<sup>1</sup>

<sup>1</sup>Physics and Astronomy, Brigham Young University, BYU Department of Physics and Astronomy, N283 ESC, Provo, UT 84602, Provo, UT, 84606

<sup>2</sup>NASA Goddard Space Flight Center, Materials Engineering Branch, Mailstop 541.0, Greenbelt, MD, 20771

# ABSTRACT

Making semiconductor devices based on single-walled carbon nanotubes (SWCNT) is one of the more compelling potential applications of these long but ultrathin structures. We see asymmetric voltage-current behavior across a random network of SWCNTs contacted by asymmetric metal electrodes (Au/Al). No effort was made to align the SWCNTs or to eliminate metallic nanotubes in our devices, procedures which are common in other devices [1]. Current rectification was, nonetheless, observed in the source-drain bias range of -3V to +3V. Rectification was somewhat surprising since, although metallic tubes are in the minority (~ 1/3), they could potentially act as shunts and mask the electric properties of the semiconducting majority. No correlation between electrode spacing and current rectification was observed. The lowest leakage current measured was 1% of the maximum current carrying capacity. Maximum forward-biased current capacities range between  $8\mu$ A and  $841\mu$ A.

### **INTRODUCTION**

Diodes and transistors are the building blocks of modern electronics. Ever since their invention, technologists have tried to put more and more transistors into smaller and smaller areas. Silicon is the standard material for building transistors, but it is being pushed to its limits. In order to continue progression into the nanoelectronic regime it is necessary to find a replacement for silicon [2].

Carbon nanotubes (CNTs) are an excellent replacement candidate for several reasons. One particularly promising characteristic of CNTs is their near ballistic transport [3], making them a very low-power alternative. Also, there is no chemical passivation necessary in CNTs as there is in silicon and many other materials [3]. This allows CNTs to be used with a variety of different insulators including flexible substrates [4]. Another advantage is the current densities CNTs can withstand. They have been shown to exhibit current densities as high as  $10^9$ A/cm<sup>2</sup> as compared to  $10^3$ A/cm<sup>2</sup> for silicon [3]. CNTs also have very large mobility which can lead to high-speed devices [5].

One major obstacle to the integration of nanotubes in electronics is the present inability to control their conduction properties during the growth process. One way to harness the compelling characteristics of CNTs without many of the difficulties associated with them is by utilizing CNT networks. No nanotube isolation or alignment is necessary. As-grown nanotube networks consist of 1/3 metallic tubes and 2/3 semiconducting tubes [6]. In spite of their metallic components, the network as a whole acts as p-type semiconductor [4]. Additionally, very low CNT-CNT junction resistances between semiconducting tubes result in only minor reductions in current [7]. The following experiment shows that carbon nanotube networks provide a simple and inexpensive way to implement CNTs into macroelectronics. Five devices on two different chips were tested and their electronic properties characterized.

#### **DEVICE FABRICATION**

The device preparation process consists of three main steps: iron catalyst deposition, nanotube-mat growth, and electrical-contact deposition. The SWCNTs were grown using an iron catalyst, chemical vapor deposition (CVD) process. The devices were fabricated on a 1cm<sup>2</sup> substrate of single crystal silicon (100) orientation with an approximate 500nm-thick thermal oxide. As discussed below, the silicon substrate is degenerately doped and can be used as a gate electrode. This process was developed at the Goddard Space Flight Center (GSFC) but has been successfully replicated at Brigham Young University (BYU). The fabrication process is outlined in general and only important differences in processing between the two locations are noted.

In order to grow nanotubes a very thin layer of iron catalyst is required. This layer is on the order of 1 nm. Conventional thermal evaporation, with the substrate facing the source, presents several difficulties in achieving ultrathin films. These difficulties are discussed in the literature [6]. In order to avoid both the cost and difficulty associated with this method we employed a method developed at the GSFC known as indirect evaporation [6].

In contrast to traditional, direct thin-film evaporation, indirect evaporation was accomplished by orienting the targeted surface of the substrate *away* from the iron source. The direct path from the source to the substrate was blocked by the sample holder, and no shutter was used. Iron was evaporated at a rate of 0.05nm/s to a thickness of 1-1.5nm according to the thickness monitor, which was water cooled. Iron reached the targeted surface through collisions with nearby surfaces within the chamber and, to lesser extent from residual gas molecules. It should be noted that the thickness measured by the thickness monitor is necessarily much greater than the actual thickness on the targeted surface. The chamber pressure was approximately 10<sup>-6</sup> Torr at the beginning of the iron deposition. This method has been successfully implemented at GSFC and at BYU, demonstrating the robustness of the technique to variations in experimental

4

conditions. Successful growths have also been achieved with a wide range of different crystalmonitor thicknesses (1.5-8nm).

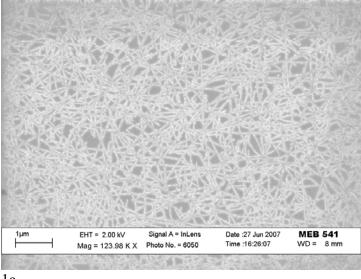

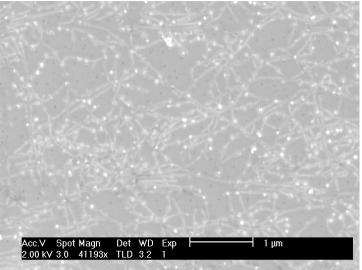

Following the catalyst deposition, the nanotubes were grown in a CVD furnace by flowing carbon rich gases under high temperatures. The initial devices were fabricated at GSFC. The substrate was placed in a quartz boat, catalyst side up, and inserted into a 1" quartz tube in a 3zone tube furnace (Lindberg, model number 55367) with a 58434-P temperature controller. Subsequent devices were fabricated entirely at BYU; the nanotubes for these devices were grown in a single-zone furnace using the same process. After purging atmospheric gases with flowing Ar, the substrate was heated to 950°C [6]. After a 5-minute soak in a hydrogen atmosphere, SWCNT growth was achieved by flowing methane, ethylene, hydrogen and humid argon (bubbled through water) over the substrate for 5 minutes [8]. (Flow rates were 1200, 50, 2000 and 730 sccm, respectively). The resulting growth networks were then imaged via scanning electron microscopy (SEM), equipped with an in-lens detector, for qualitative comparisons. The in-lens detector is known to cause nanotubes to stand out but also exaggerate their width [9]. At GSFC a LEO Supra 50VP system was used, and at BYU we used a FEI XL30 SFEG. The reproducibility of the indirect catalyst deposition method suggests that it is an inexpensive and effective means of reliably growing carbon nanotube networks; the techniques and results shown herein are expected to be largely facility-independent. Figures 1a and 1b are SEM images of nanotube growths, from both facilities.

Following the nanotube growth and its verification through SEM, asymmetric metal contacts were deposited as reported in the literature [11]. We deposited aluminum to act as the rectifying contact and gold as the ohmic contact [12]. This combination has been shown to rectify current when a single SWNT was contacted between the two electrodes [11]. Our goal was to achieve similar rectifying behavior using a composite network of overlapping semiconducting and metallic tubes. Using parallel-bar grids (Electron Microscopy Sciences) and

5

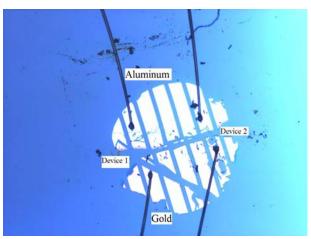

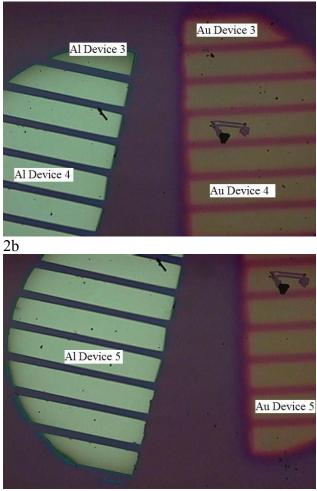

covering half of the grid with a shadow mask, we deposited a set of aluminum electrodes using thermal evaporation. We then covered the other half of the grid in order to deposit a set of gold electrodes. Figures 2a, 2b and 2c are optical images of completed devices.

After device fabrication was complete we prepared the devices for electrical characterization. First we removed the nanotubes from the perimeter of the silicon chip to prevent electrical shorting from the nanotubes to the bare silicon when performing gate voltage dependence experiments. They can be removed simply by scratching a 3mm perimeter around the edge of the silicon chip, taking care to avoid breaking through the oxide. The substrate was then attached to a chip carrier. We used silver paint in order to connect one of the inputs of the chip carrier to the substrate in order to use the silicon as a back gate. At GSFC we used a Kulicke & Soffa 3523A Digital Wire Bonder to contact the devices, while at BYU the electrodes were contacted directly using tungsten probes.

#### **EXPERIMENT AND DISCUSSION**

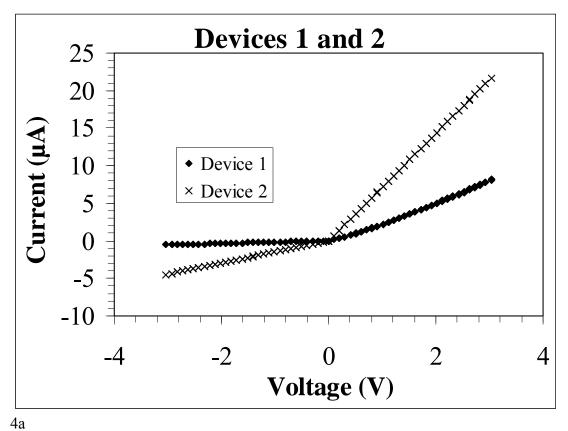

After the devices were fabricated we took pictures of the samples to relate devices' electronic properties with their physical characteristics. Using a probe station we plotted output current versus source-drain voltage in the range -3 V to 3V. Two or three repeated sweeps were conducted to ensure reproducibility. This scan covers both the forward- and reverse-bias modes of these devices. Forward bias is defined as the case when the gold electrode is positive with respect to the aluminum electrode. We expected to see Schottky diode-like behavior similar to that reported in the literature [11]. Current rectification was observed but did not resemble typical nonlinear Schottky diode behavior. It was linear in forward bias.

Figure 4 shows the current-voltage characteristics of two devices from a single silicon chip (figure 2a). Data from devices 1 and 2 are represented in figure 4 by squares and x's, respectively. Device 1 has an electrode spacing of 289µm. The ratio of the maximum forward-bias current to the maximum reverse-bias current is 20, commonly known as the on/off ratio.

The maximum forward-bias current is  $8\mu A$ . Device 2, with an electrode spacing of  $219\mu m$ , only exhibited an on/off ratio of 5 and a maximum forward-bias current of  $22\mu A$ .

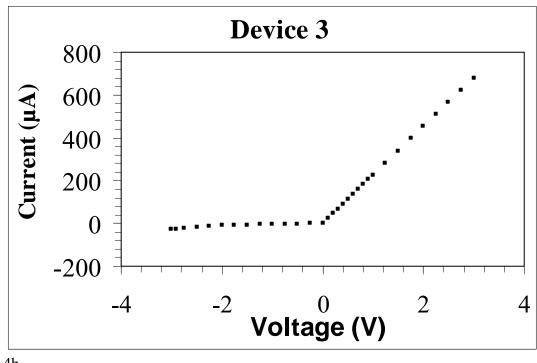

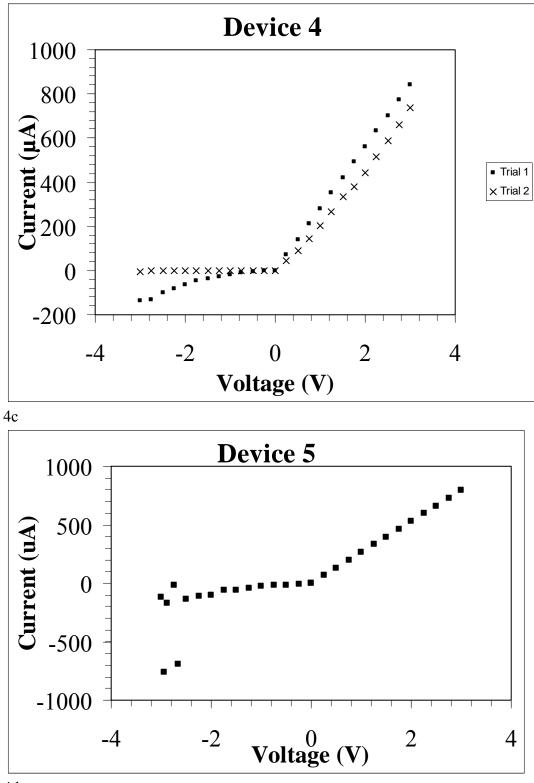

In addition to the two devices fabricated at GSFC, four additional devices were fabricated at BYU on a single substrate (figures 2b and 2c). The processing on these devices was similar to the other devices but there are some important differences. The thicknesses of the aluminum and the gold are visibly thicker than those of previous devices regardless of the similar thicknesses reported by the thickness monitors (perhaps due to discrepancies in tooling factors). Additionally, the thickness of the gold and aluminum are not equal. There is about twice as much aluminum as gold based on comparing thickness monitor readings. This difference accounts for the poor focusing in figures 2b and 2c. None of these devices were wire bonded they were characterized using tungsten probe needles. Another difference between the two sets of devices is the nanotube network itself. The nanotube mat used for devices 3-6 is significantly less dense and there are larger iron-containing particles on the surface. These particles appear as bright spots when close to the conducting nanotubes and dark spots when farther away [6]. (Compare figures 1a and 1b). Lastly, the contacts were deposited so that the distance between the electrodes increased from top to bottom. (See figure 2b and 2c) The higher on/off ratio for the larger electrode spacing in devices 1 and 2 above suggested that this parameter might be important. The I-V plots of these devices are found in figures 4b and 4c.

Although none of the devices have I-V curves typical of conventional Schottky diodes, two distinct tests reinforce our conclusion that these are semiconducting devices. First, current rectification as displayed in figure 4, is indicative of the semiconducting nature of the two devices. Furthermore, device 1 exhibited gate-voltage dependence in the following experiment.

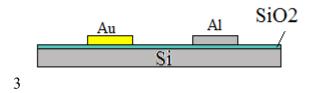

Applying a gate voltage to this device makes it act as a transistor. We applied a gate voltage by contacting the silicon and relying on the silicon dioxide layer to act as the isolating dielectric between the applied voltage on the back and the SWCNT device on the front (figure 3).

The I-V response of device 1 was measured by applying a variable gate voltage with a fixed source-drain voltage. All of the measurements were made at a constant source-drain voltage of +3V. The gate voltage was varied from -10V to 10V.

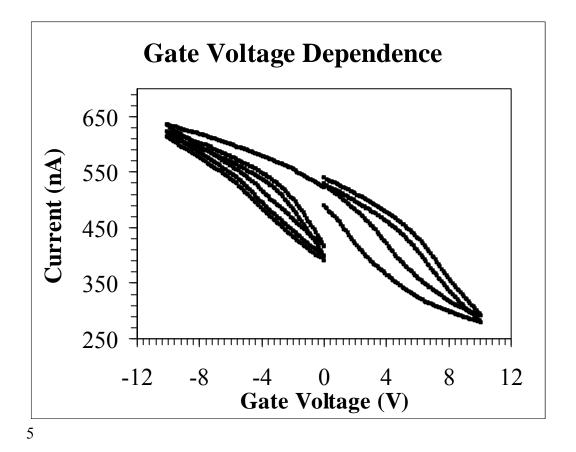

Figure 5 shows the current as a function of gate voltage. As the gate voltage increases in the positive direction, the current decreases. The gate bias produces an electric field which depletes the semiconducting nanotube mat of carriers. Fewer carriers mean less current. As the voltage increases in the negative direction, more carriers are introduced and so the current increases. Another prominent feature in figure 5 is hysteresis. That the current-voltage relationship is multivalued is evidence of charge trapping in the nanotube structure [13].

Here, we estimate the carrier mobility of our nanotube network devices to quantify the degradation of device properties due to ensemble effects, compared to optimized device performance. We can determine the field effect mobility by examining the change in device conductance with gate voltage, according to

$$\mu = \frac{L}{c_g} \frac{\partial G}{\partial V_g},\tag{1}$$

where  $\mu$  is the field effect mobility, *L* is the device length,  $c_g$  is the gate capacitance per unit length, *G* is the device conductance, and  $V_g$  is the gate voltage. For a single nanotube and a similar gate dielectric and geometry,  $c_g$  has been reported as190 fF/cm. The capacitance must be scaled according to the number of nanotubes, semiconducting and metallic, forming the device. Based on scanning electron micrographs, we estimate the average number of nanotubes contributing to the device to be of order 2000. Adding the parallel capacitances together, we obtain a total capacitance per unit device length to be 190 fF/cm x 2000 nanotubes = 380 pF/cm. For a device length of 300 µm, then, we can estimate that device 1 exhibits a field effect mobility of 0.268 cm<sup>2</sup>/V-s which is comparable to other organic thin film transistors formed on an SiO2 substrate [14].

# CONCLUSION

Diode SWCNT devices have been fabricated using Au and Al, as the asymmetric metal contacts, and a random network of metallic and semiconducting nanotubes as the the device channel. These devices exhibit current rectification and current output dependency on a back-gate voltage was observed. An on/off ratio of 108 was achieved in the best case, as well as current capacities as high as  $841\mu$ A for a source-drain bias in the range of -3 to +3V. No correlation between electrode spacing and current rectification was observed.

# ACKNOWLEDGMENTS

We would like to acknowledge the following organizations for their financial support which made the success of this project possible: the Rocky Mountain Space Grant Consortium (summer 2007), the ESMD Faculty/Student mentor program, and the BYU College of Physical and Mathematical Sciences. Likewise, without the support of the following individuals this research could not have been conducted: Jon Brame, Johnathan Goodsell, Rachel Bis, Dewey Dove, Chris O'Neill and other members of Goddard Space Flight Center Code 541. References:

1. S. J. Kang, C. Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, Slava V. Rotkin and J. A. Rogers, Nature Nanotechnology, 230 (2007) 2.

2. G. F. Close, S. Yasuda, B. Paul, S. Fujita, and H.-S. P. Wong, Nano Lett. 706 (2008) 8

3. P. Avouris, J. Appenzeller, Richard Martel, And S. J. Wind. Proceedings of the IEEE. 91, 11 (2003)

4. E. S. Snow, J. P. Novak, M. D. Lay, E. H. Houser, F. K. Perkins, and P. M. Campbell, J. Vac. Sci. Technol. 1990 (2004) B 22.4.

5. T. Durkop, S. A. Getty, Enrique Cobas, and M. S. Fuhrer, Nano Lett. 35 (2004) 4.

6. J. Goodsell, S. A. Getty, J. Brame, and D. D. Allred, The Journal of the Utah Academy of Sciences, Arts, and Letters, **84** (2007), in press.

7. M. S. Fuhrer, J. Nygard, L. Shih, M. Forero, Y. G. Yoon, M. S. C. Mazzoni, H. J. Choi, J. Ihm, S. G. Louie, A. Zettl, and P. L. McEuen, Science **288**, 494 (2000).

8. K. Hata, D. N. Futaba, K. Mizuno, T. Namai, M. Yumura, S. Iijima. Science 306, 1362 (2004).

9. T. Brintlinger, Y.-F. Chen, T. Durkop, E. Cobas, M. S. Fuhrer, J. D. Barry, and J. Melngailis, *Appl. Phys. Lett.* **81**, 2454 (2002).

10. N. Hamada, S. Sawada, and A. Oshiyama, Phys. Rev. Lett. 68, 1579 (1992).

11. C. Lu, L. An, Q. Fu, J. Liua, H. Zhang and J. Murduck. Appl. Phys. Lett. 88, 133501 (2006)

12. S.M. Sze, Semiconductor Devices: Physics and Technology, 2nd ed. (John Wiley & Sons, Inc, New Jersey, 2002), p. 225-236.

13. M. S. Fuhrer, B. M. Kim, T. Durkop, and T. Brintlinger. Nano Lett. 755 (2002) 2.

14. C. D. Dimitrakopoulos and P. R. L. Malenfant. Adv. Mater. 14, 100 (2002) 2

**Figure 1a:** Carbon nanotube network used to fabricate devices 1 and 2. Single wall carbon nanotube mat grown using an indirect iron catalyst [1]. Tubes were deposited by CVD of methane, hydrogen, ethylene and humid argon at 950 C for 5 minutes. In-lens configuration is known to highlight nanotubes but their width is not well represented in the image.

**Figure 1b:** Carbon nanotube network used to fabricate devices 3, 4 and 5. Note the significantly lower density of nanotubes and the large iron particles found in the mat. The perceived difference in width should not be considered accurate because this feature is highly dependent on the SEM settings.

**Figure 2a:** Devices 1 and 2 which exhibited on/off ratios of 22 and 5, respectively. Al and Au electrodes are identified. The mat of nanotubes covers the entire pictured area and is below the deposited electrodes.

**Figures 2b:** Devices 3 and 4 are pictured. The electrodes which define each device is labeled. "Au Device 3" is the gold electrode of device 3. The other electrodes are labeled similarly. Note the variation in spacing between the electrodes of the different devices.

**Figure 2c:** Device 5 is pictured. The electrodes which define this device are labeled. "Au Device 5" is the gold electrode of device 5. The other electrode is labeled similarly.

**Figure 3:** Cross section of final device. The nanotube mat is not pictured but is a thin layer on top of the  $SiO_2$  layer and beneath the Au and Al contacts. There are two modes for making electrical measurements using this structure. In the first mode, Au and Al electrodes (source-drain) are contacted and current is measured as the source-drain voltage is varied. In the second mode the underlying silicon is contacted and acts as a gate, setting up an electric field which depletes or injects current carriers into the nanotubes depending on its bias.

**Figure 4a:** Electrical characterization of devices 1 and 2 as pictured in fig 1. On/off ratios 20 and 5 respectively. Devices 1 and 2 achieved maximum current capacities of 8  $\mu$ A and 22  $\mu$ A, respectively.

**Figure 4b:** Electrical characterization of device 3 as pictured in fig 1. On/off ratio of 27. The maximum current capacity is 679  $\mu$ A. Note the drastic difference in current capacity as compared to devices 1 and 2.

**Figure 4c:** Electrical characterization of device 4. The figure displays two subsequent trials. On/off ratio of trial 1 is 6 and the on/off ratio of trial 2 is 108. The maximum current capacity is 841  $\mu$ A in the first trial and 735  $\mu$ A in the second. Note the drastic difference in rectification between the two trials.

**Figure 4d:** Electrical characterization of device 5. On/off ratio is difficult to determine because of the dramatic variations in the reverse bias region. The maximum current capacity is  $794 \mu A$ .

**Figure 5:** Gate voltage dependence of diode device 1 (figure 1a). The first thing to note is that current increases towards the left and falls towards the right. As the gate voltage increases negatively more carriers are drawn into the conduction band and current increases. In contrast, as

the gate voltage is increased positively fewer carriers are available to carry current. That the current-voltage relationship is multivalued is evidence of charge trapping in the nanotube structure [13].

# Figures

1a

1b

2a

2c

4b

4d